Cache com Mapeamento Direto

O cache com mapeamento direto é uma das formas mais simples de organização de memória cache nos sistemas computacionais. Nessa estrutura, a memória RAM é dividida no mesmo número de linhas disponíveis no cache.

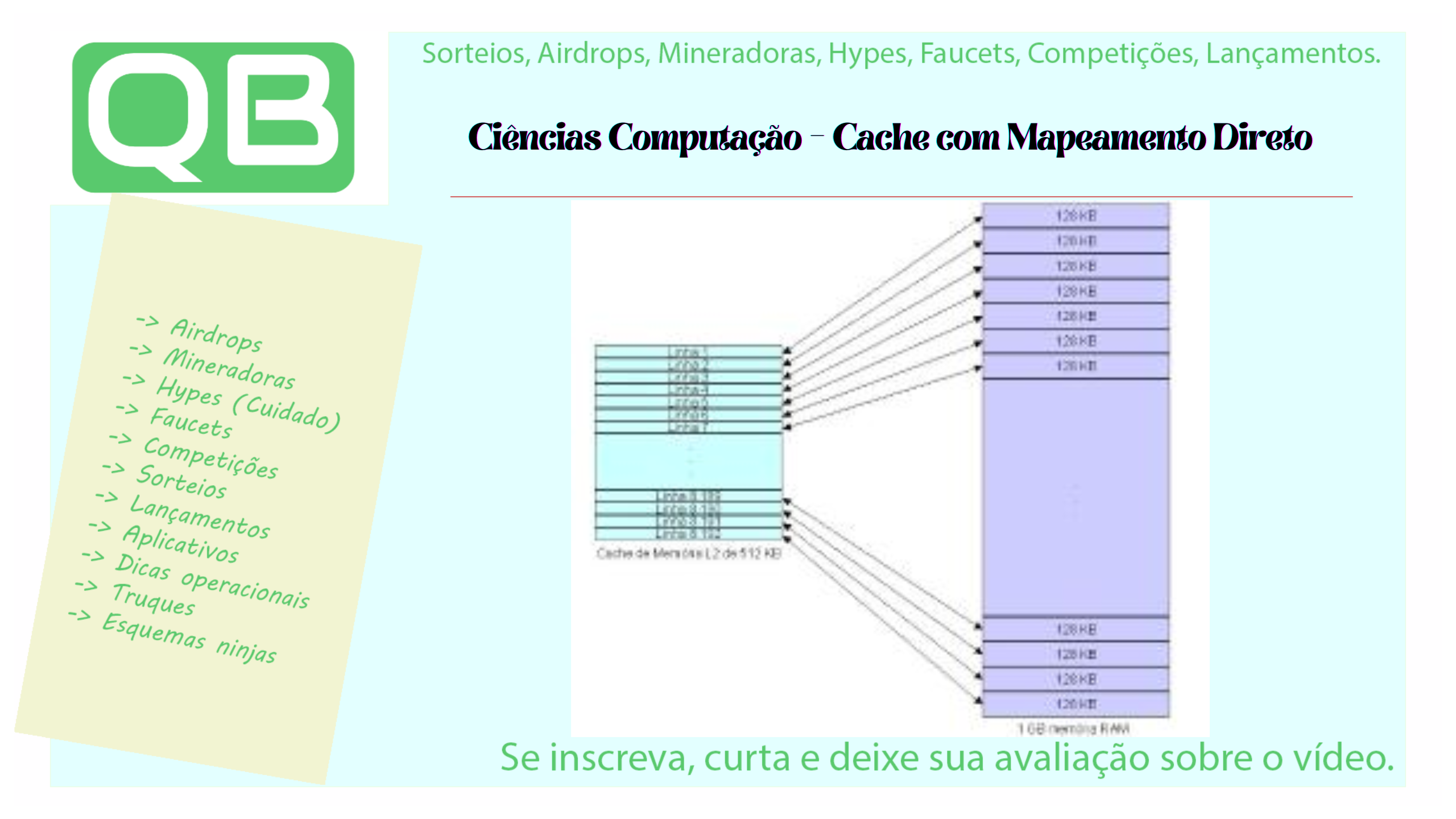

Por exemplo, se temos um computador com 1 GB de memória RAM (equivalente a 230 bytes) e um cache de memória dividido em 8.192 linhas, cada bloco de memória corresponderá a aproximadamente 128 KB (1.073.741.824 / 8.192 = 131.072 bytes).

Como o mapeamento direto funciona

Esse método associa cada bloco de memória RAM a uma única linha do cache. Assim, ao acessar um endereço da RAM (por exemplo, endereço 1000), o controlador de cache carrega uma linha de dados correspondente (por exemplo, de 1000 a 1063) e armazena no cache.

Se o processador voltar a solicitar o mesmo endereço ou qualquer outro dentro da faixa armazenada, o acesso será feito diretamente no cache, aumentando a velocidade do sistema.

Colisões e conflitos no cache

Um dos grandes problemas do mapeamento direto é a possibilidade de conflitos. Se dois endereços diferentes da memória RAM forem mapeados para a mesma linha do cache, eles não poderão coexistir simultaneamente.

Continuando nosso exemplo, se o processador solicita o endereço 1000 e, em seguida, o endereço 2000, que também está mapeado para a mesma linha, ocorre uma substituição no cache. Isso é conhecido como colisão de cache.

Impacto em loops e desempenho

Esse tipo de problema se torna mais evidente durante a execução de loops (repetições) maiores que a linha do cache.

Por exemplo, se um loop de código percorre os endereços de 1000 até 1100:

- Inicialmente, o cache carrega os endereços de 1000 a 1063.

- Quando chega no endereço 1100, o cache precisa carregar de 1100 a 1163, eliminando a faixa anterior.

- Ao voltar para 1000, ocorre novamente um carregamento direto da RAM, e esse ciclo se repete.

Se esse loop for executado 1000 vezes, o processador fará 1000 acessos diretos à RAM, impactando seriamente o desempenho.

Por que o mapeamento direto caiu em desuso?

Apesar de ser de fácil implementação, o mapeamento direto é menos eficiente comparado a outras técnicas de cache, como:

- Mapeamento associativo

- Mapeamento associativo por conjunto (set-associative)

Essas abordagens oferecem maior flexibilidade e diminuem significativamente os conflitos de cache, sendo amplamente utilizadas nos sistemas modernos.

Resumo das vantagens e desvantagens

| Vantagens | Desvantagens |

|---|---|

| Fácil de implementar | Alta taxa de colisão |

| Baixo custo de hardware | Ineficiente em loops grandes |

| Menor consumo de energia | Desempenho inferior |

Conclusão

O mapeamento direto ainda é útil para estudos e implementação em arquiteturas simples. Contudo, para aplicações modernas que exigem alta performance, como jogos, ciência de dados ou inteligência artificial, são utilizados métodos mais eficientes e inteligentes de cache.

Recomendação: conheça outras técnicas de cache e compare os desempenhos para escolher o modelo ideal para seu projeto.

Exemplo de ferramenta para estudo

Para organizar scripts e códigos ao desenvolver um simulador de cache ou estudos relacionados, utilize ferramentas como o HTML Cleaner, gratuita e funcional.

Importante para projetos com fins lucrativos

Se estiver desenvolvendo software ou projeto que visa retorno financeiro, lembre-se: decisões de investimento e monetização devem sempre ser avaliadas individualmente. Não invista em algo que você não entende completamente. Faça uma análise criteriosa antes de investir tempo ou dinheiro.

Comentários

Comente só assim vamos crescer juntos!